新智元原创

修改:元子,白峰

就在疫情迸发前一个月,教育部宣告一篇文章《打响“卡脖子”技能攻坚战》。

现在有35项卡脖子技能,光刻机和芯片赫然在列。华为、阿里、百度纷繁推出自研芯片。在国家的扶持和本钱的推动下,国内芯片企业遍地开花。一时之间,似乎一切厂商都宣告要做芯片;大厂都在做,小厂也要做。

可是一场出人意料的疫情打乱了一切人的节奏。疫情之下,芯片工业发展怎么?

台积电:疫情问题不大,5nm现已组织,3nm下一年量产

尽管疫情冲击了整个经济大环境,可是台积电CEO魏哲家却仍旧信心十足。他表明,遭到5G及高效能运算(HPC)对先机制程的微弱需求,台积电的方案没有遭到太大影响,一切都在墨守成规的进行中。

台积电7nm订单足够。业界预算其累积出资达250-300亿美元,月产能约为100000片,一统7nm江湖,台积电估计其将奉献30%收入。

6nm制程将依照方案于年末完成量产,比7nm加强版多了1层EUV(极紫外光刻)光罩层。

5nm也已准备好下半年进行量产。比较长辈们,5nm制程增加了更多EUV光罩层,下半年开端进入量产,预期收益将占总收入的10%。业界预算其出资达250亿美元,月产能50000片,后续将扩大至70000-80000片。

更重要的是,3nm也肯定没因疫情而推迟的意思。依据gizmochina报导,本年建厂、下一年试产,2022年下半年量产。业界预算其出资约为200亿美元。

纵观全球半导体制程玩家,现在仅剩鼎足之势:英特尔、三星和台积电。而其间真实卯着劲在攻坚3nm的,其实只要三星和台积电两家罢了。从市场占有率来看,台积电暂时抢先。

3nm遭到重视,2nm负重致远,1nm遥遥无期

业界期望从3nm开端,从当今的finFET晶体管过渡到万能门FET。在2nm乃至更高的制程下,业界正在研讨当时和新版本的万能门晶体管。

2nm节点及更高节点的作业发展顺畅,但应战很多,不确定性也渐渐变得高。

3nm和2nm技能现已定于2022年和2024年推出,而1nm及更先进制程工艺仍在研制中,离商用仍旧悠远。

为什么从5nm到3nm,以及再往后难度猛增?这儿咱们要简略回忆一下制程的常识。

以10nm制程为例,是指在芯片中线最小能做到14nm的尺度。下图为传统晶体管的结构,为了削减能耗,咱们要想办法缩小晶体管尺度。

晶体管的作业原理,通电1断电0,就能完成计算机的运算。Gate端施加电压,电流就会从Drain端到Source端。

减缩元器材之间的间隔之后,晶体管之间的电容也会更低,电容低了就能频频开关而且能耗会变小,芯片才能够在速度更快的一起,做到愈加省电,而且缩短间隔后,相同的面积上能够放置更多的晶体管。所以芯片厂都在尽或许的下降芯片制程。

原子的巨细大约为0.1nm,10nm工艺就要确保一条线只要不到100个原子,一个原子出问题,整个产品就报废了,产品的良率会打扣头。

finFET才能探底,新技能散热问题没有解决

晶体管是芯片中的要害构建模块之一,可在设备中供给开关功用。市场预测5nm的命运或许步10nm后尘,成为从6nm到3nm的过渡。

跟着芯片转向3nm及更先进的制程,finFET才能现已探底,部分代工厂期望在2022年迁移到称为纳米片FET的下一代晶体管。纳米片FET归于所谓的gate-all-around FET。

纳米片FET是finFET的扩展。它的旁边面是finFET,栅极包裹着它。纳米片将呈现在3nm处,并或许延伸至2nm乃至1nm。

还有其他gate-all-around类别,例如,Imec正在开发2nm的forksheet FET、Complementary FET (CFET)。

在forksheet FET中,nFET和pFET都集成在同一结构中,具有42nm的触摸栅距离(CPP)和16nm的金属距离,答应更严密的n到p距离并削减面积缩放。

CFET由两个独自的纳米线FET(p型和n型)组成。Imec的董事介绍,CFET经过“折叠”pFET器材上的nFET将电池有用面积减小了两倍,可是散热成了问题。

光刻技能是在芯片上构图微细图形的技能,有助于完成芯片缩放。可是在5nm工艺下,当时的根据光学的193nm光刻扫描仪现已极力了。

在3nm及以上的工艺中,芯片制造商或许需求一种称为高数值孔径EUV(high-NA EUV)的EUV光刻新技能。芯片商期望这种既杂乱又贵重的技能能够在2023年研制成功。

从原子层蚀刻到新一代分子水平加工

当今的芯片是运用各种原子级处理东西出产的。一种称为原子层堆积(ALD)的技能可一次将资料堆积一层。

原子层蚀刻(ALE)是一项相关技能,能够原子级去除方针资料。ALD和ALE均用于逻辑和存储器。

区域挑选堆积是一种先进的自对准构图技能,从理论上讲,挑选性堆积可用于在金属上堆积金属,在器材上的电介质上堆积电介质。

现在适用于3nm及以上工艺中的ALD和ALE高档版仍在研制中。

行将呈现的另一项技能是分子层蚀刻(MLE),是有机/无机杂化资料的延伸。关于半导体职业来说,它供给了一种办法来进行各向同性的资料复原,这些资料能够用作光刻的掩模。

计量学也面对一些应战。现在,芯片制造商运用各种体系(例如CD-SEM,光学CD等)来丈量结构。CD-SEM进行自上而下的丈量。光学CD体系运用偏振光来表征结构。

可是,根据晶圆厂的CD-SAXS的问题在于X射线源有限且速度慢,这会影响吞吐量,而且本钱或许要贵5倍或10倍。

缩放本钱贵重功用优势削减,芯片封装带来期望

IC缩放是推动规划的传统办法,它依赖于缩小每个节点上的不同芯片功用并将它们封装到单片式芯片中。可是关于许多人来说,IC缩放变得太贵重了,而且每个节点的功用和功耗优势都在削减。

这促进封装厂和铸造厂经过改进设备之间的衔接,并进步封装自身的密度来进一步提高已封装设备的速度。

台积电(TSMC)尽力将小芯片嵌入在线前端(FEOL)的封装中便是一个很好的比如。代工厂方案将先进的混合键合技能用于所谓的集成芯片体系(SoIC)。

这将比运用硅中介层将芯片衔接在一起要快得多。

2024爱企查毕业季校园行:构建诚信就业市场,为成电、广大学子保驾护航

2024爱企查毕业季校园行:构建诚信就业市场,为成电、广大学子保驾护航 淘宝百亿补贴618期间上线惊喜闪购,梦里啥都有真香!

淘宝百亿补贴618期间上线惊喜闪购,梦里啥都有真香! 蔡怀军分享芒果文化与科技融合的前瞻思考

蔡怀军分享芒果文化与科技融合的前瞻思考 全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量”

全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量” “千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州

“千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州 加速创“芯” 西门子EDA技术峰会在沪举办

加速创“芯” 西门子EDA技术峰会在沪举办 DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节

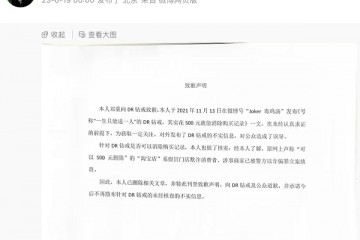

DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节 传谣“DR购买记录可删”者向DR和公众道歉

传谣“DR购买记录可删”者向DR和公众道歉